自动驾驶AI芯片选型的20个关键指标

中央控制器作为自动驾驶核心部件,作为自动驾驶的“大脑”端,通常需要外接多个摄像头、毫米波雷达、激光雷达,以及IMU等设备,完成的功能包含图像识别、数据处理等。

域控制器作为一个智能硬件,为了完成复杂的AI计算和智能控制,硬件层面需要承担环境感知和深度学习等超大算力需求的AI处理芯片、负责控制决策和逻辑运算的CPU、以及负责功能安全和车辆控制的MCU;软件层面包括操作系统、中间件以及应用层AI算法等。

硬件层面的三部分芯片或者叫三颗重要芯片:

第一部分通常是GPU或TPU,承担大规模浮点数并行计算需求,主要用于环境感知和信息融合,包括摄像头、激光雷达等传感器信息的识别、融合、分类等,如Xavier的GPU单元、昇腾310。

第二部分大多为ARM架构,类似于CPU,主要负责逻辑运算和决策控制,处理高精度浮点数串行计算。

第三部分主要负责可靠性和车辆控制,也就是功能安全和冗余监控作用,不要求很高的算力,但是可靠性必须要有保障,ISO26262等级要求达到ASIL-D,目前用的较多的就是Infineon的TC297或者TC397。

软件层面应用层AI算法一般由造车企业或主机厂自行研发,这是体现车辆性能和的所在;中间件一般由域控制器开发商提供,类似于ROS,主要包含一些接口驱动和对于操作系统的优化部署。

操作系统方面,华为采用自研鸿蒙系统,并且MDC平台支持兼容Adaptive AUTOSAR;QNX是目前车规级的最佳也是唯一选择,但是面临高昂的费用;Linux和Autoware 由于开源反而获取了最多的用户,尤其是Linux,借助其强大的工程师基础和生态,加之ROS的多年应用基础,基于Linux内核的操作系统目前很受欢迎。

关于自动驾驶AI芯片选型

目前市面上可供选择的AI芯片并不多,尤其是达到量产状态的,只有特斯拉、NVIDIA、Mobileye了。除了特斯拉自研自用不对外,其他品牌目前都可以通过合作开发方式拿到测试样件。

以NVIDIA Xavier为例,相对而言,由于NVIDIA Xavier推出较早,并且生态布局相对完善,对于开发者来说可以快速构建系统和开发AI应用,因此基于Xavier模组进行域控制器设计的企业不在少数。

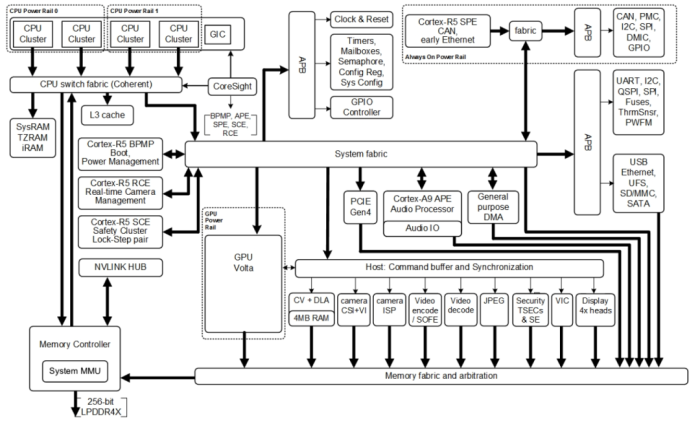

XavierSoC最高算力可达30TOPs,内有Valta TensorCore GPU,八核ARM64 CPU,双NVDLA 深度学习加速器,图像处理器,视觉处理器和视频处理器等六种不同的处理器,使其能够同时、且实时地处理数十种算法,用于传感器数据处理、环境感知、定位和绘图以及路径规划。

芯片内部结构如下图所示:

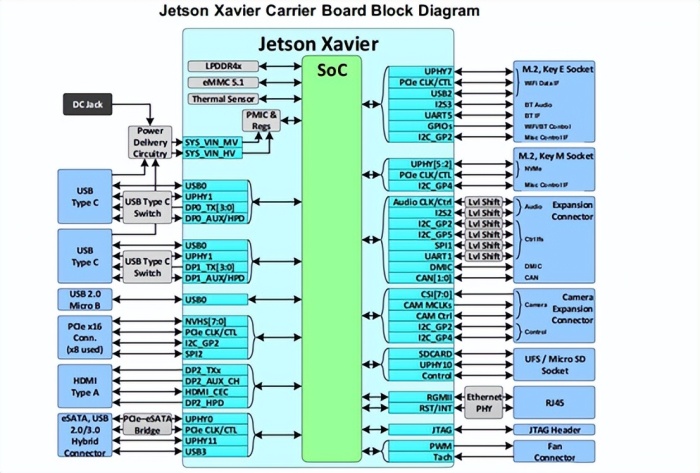

NVIDIA 提供的Xavier为核心模组,其接口如下图所示:

——芯片的关键指标:

1)Core:内核通常是空间中心。一方面便于自动驾驶控制器和外围传感器、执行器通讯,同时也用外围来保护它。core强调运行态,通常出现的core-down,是指cpu计算上出现问题了,core强调的是自动驾驶控制器整体对外功能中的核心功能。

2)DMIPS:主要用于测整数计算能力。包含每秒钟能够执行的指令集数量,以及其这些指令集在实现我的测试程序的时候,每秒钟能够实现的工作数量,这个能力由cpu的架构,内存memory的访问速度等硬件特性来决定。它是一个测量CPU运行相应测试程序时表现出来的相对性能高低的一个单位(很多自动驾驶芯片评估场合,人们习惯用MIPS作为这个性能指标的单位)。

3)Memory:存储器管理单元的主要功能包括:虚拟地址到物理地址映射、存储器访问权限控制、高速缓存支持等;

4)DataFlash:DataFlash是美国ATMEL公司推出的大容量串行Flash存储器产品,采用Nor技术制造,可用于存储数据和程序代码。与并行Flash存储器相比,所需引脚少,体积小,易于扩展,与单片机或控制器连接简单,工作可靠,所以类似DataFlash的串行Flash控制器越来越多的用在自动驾驶控制器产品和测控系统评估中。

5)ISP:ISP作为视觉处理芯片核心,其主要功能包括 AE(自动曝光)、AF(自动对焦)、AWB(自动白平衡)、去除图像噪声、LSC(Lens Shading Correction)、BPC(Bad PixelCorrection),最后把 Raw Data 保存起来,传给 videocodec 或 CV 等。通过 ISP 可以得到更好的图像效果,因此在自动驾驶汽车上对ISP的要求很高,比如开始集成双通道甚至三通道的 ISP。一般来说 ISP 是集成在 AP 里面(对很多 AP 芯片厂商来说,这是差异化竞争的关键部分),但是随着需求的变化也出现了独立的 ISP,主要原因是可以更灵活的配置,同时弥补及配合 AP 芯片内 ISP 功能的不足。

6)算力:自动驾驶的实现,需要依赖环境感知传感器对道路环境的信息进行采集,将采集到的数据传送到汽车中央处理器进行处理,用来识别障碍物、可行道路等,依据识别结果,规划路径、制定车速,自动控制汽车行驶。整个过程需要在一瞬间完成,延时必须要控制在毫秒甚至微秒级别,才能保证自动驾驶的行驶安全。要完成瞬时处理、反馈、决策规划、执行的效果,对中央处理器的算力要求非常高。

在自动驾驶中,最耗费算力的当属视觉处理,占到全部算力需求的一半以上,且自动驾驶级别每升高一级,对计算力的需求至少增加十倍。L2级别需要2个TOPS的算力,L3需要24个TOPS的算力,L4为320TOPS,L5为4000+TOPS。

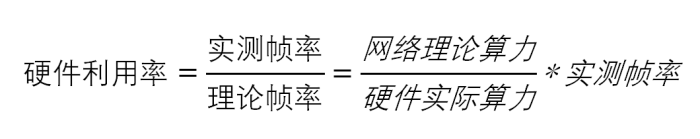

光有算力还不够,考虑汽车应用的复杂性,汽车处理器还需要同时考虑算力利用率、是否通过车规和安全标准等。算力理论值取决于运算精度、MAC的数量和运行频率。

理论算力是根据Net卷积层的乘法运算累加得出,卷积层中的每次乘加(MAC)算成两个OPS,卷积运算量占DL NET的90%以上,其它辅助运算或其它层的运算忽略不计,SSD所有卷积层乘法运算总数是40G MACs,所以理论算力是80GOPS。

其中,

真实值和理论值差异极大,考虑其它运算层,硬件实际利用率要高一些。决定算力真实值最主要因素是内存( SRAM和DRAM)带宽,还有实际运行频率(即供电电压或温度),还有算法的batch尺寸。

7)功耗:在最高性能模式下,如果自动驾驶控制器的芯片功耗级别较高,即便其自身性能强劲,但也会引发某些未可预知的隐患,如发热量成倍增加,耗电率成倍增加,这些结果尤其对于新能源车型来说也毫无疑问是颗“核弹”。因此,我们在前期自动驾驶芯片设计中需要充分考虑其功耗指标。

8)3D GPU:GPU是基于大的吞吐量设计,用来处理大规模的并行计算。GPU的控制单元可以把多个的访问合并成少的访问。GPU将更多的晶体管用于执行单元,而非像CPU那样用作复杂的数据cache和指令控制。由于GPU具有超强的浮点计算能力,可用于在智能汽车前端的图像或视频处理领域的应用,也越来越多地应用在中央控制器高性能计算的主流设计中。

9)丰富的IO接口资源

自动驾驶的主控处理器需要丰富的接口来连接各种各样的传感器设备。目前业界常见的自动驾驶传感器主要有:摄像头、激光雷达、毫米波雷达、超声波雷达、组合导航、IMU以及V2X模块等。

对摄像头的接口类型主要有:MIPI CSI-2、LVDS、FPD Link等。

激光雷达一般是通过普通的Ethernet接口来连接。

毫米波雷达都是通过CAN总线来传输数据

超声波雷达基本都是通过LIN总线

组合导航与惯导IMU常见接口是RS232

V2X模块一般也是采用Ethernet接口来传输数据

除了上述传感器所需IO接口外,常见的其它高速接口与低速接口也都是需要的,比如:PCIe、USB、I2C、SPI、RS232等等。

10)PCIe:作为CPU的局部总线,最大的特点在于数据传输吞吐量大和延迟低。

11)SaftyGoal:功能安全目标是整个自动驾驶中央控制器的核心设计需求,由于其影响对整个自动驾驶功能设计中的单点失效分析结果,因此,在前期硬件设计中就需要充分考虑其是否能够完全满足系统对于硬件的功能安全设计需求。

12)OTA:远程升级为用户修复软件故障,大幅度缩短中间步骤的时间,使软件快速到达用户,同时可以为车辆增加新功能,拓宽 “服务”和“运营”的范畴。因此,中央控制器芯片是否支持OTA对于减少汽车制造产商和用户的成本,包括汽车制造产商的召回成本,用户的时间成本,增加用户的新鲜感,增加车辆的附加价值显得不可或缺。

13)封装类型:控制器封装尺寸的大小、引脚定义等影响整体驾驶控制器对安装形式的影响,同时影响对外围部件的连接情况分布。另外,接口是否防水,如果能防水,则控制器的安装环境可以相对更加自由。不过,目前的域控接口都是不防水的。

14)温度/电压:控制器的温度控制范围包括其存储、使用环境温度,且后期若实际车辆确认前毫米波控制器总成布置区域存储、使用环境温度高于该值,需要在该基础上进行一定程度的整改上调范围,并满足OEM要求,且供应商需要保证不因为硬件设计缺陷导致召回。特别是算力达到100以上,功耗在60W以上时,温度的上升极可能需要主动散热来确保热量可以及时的传递出去,不影响控制器的正常工作。主动散热一般包括:风扇散热、水冷散热。

15)车规与功能安全:与消费电子产品相比,汽车芯片在安全性和可靠性上有这个最高的要求。

汽车芯片长年工作在“-40℃到125℃”高低温以及剧烈震动的恶劣环境下,为了保证汽车电子产品达到对工作温度、可靠性与产品寿命的高标准质量要求,国际汽车电子协会(Automotive Electronics Council,AEC)建立了相关的质量认证标准,其中AEC-Q100是针对于车载集成电路压力测试的认证标准。AEC-Q100标准经过多年发展,已经成为汽车电子产品在可靠性和产品寿命等方面的工业事实标准。

除了满足车规级要求之外,自动驾驶芯片也需要满足由ISO 26262标准定义的“功能安全(Function Safety,简称Fusa)”的认证要求。功能安全对芯片上的设计要求是要尽可能找出并纠正芯片的失效(分为:系统失效和随机失效)。系统失效本质上是产品设计上的缺陷,因此主要依靠设计和实现的流程规范来保证,而随机失效则更多依赖于芯片设计上的特殊失效探测机制来保证。

ISO 26262对安全等级做了划分,常见的是ASIL-B和ASIL-D级别。ASIL-B要求芯片能覆盖90%的单点失效场景,而ASIL-D则要求能达到99%。芯片面积越大,晶体管越多,相应的失效率越高。

16)芯片系统:如控制器是否支持MCU+MPU的集成控制方式,还是只支持单芯片控制的形式。

17)供应链保障:较大的市场需求导致半导体供应链和产能紧缺,包括疫情在内的各种“天灾人祸”不断扰乱半导体的正常生产节奏,而需求与产能之间的矛盾在短期内难以解决。对

在全球芯片供应链如此紧张的背景下,对于域控制器供应商而言,供应链的保障也是十分的具有挑战性。整车厂在选择域控制器供应商的时候,其合作伙伴芯片厂商的供货能力也是重要的考量指标。

2022 年,芯片短缺仍在影响汽车行业,有些整车厂已经开始思考半导体供应的新思路,有的甚至绕过Tier1直接找芯片设计厂商。更深入一点的主机厂已经开始参与到芯片设计的研发流程中。比如,多家车企已经与黑芝麻、地平线这样的自动驾驶AI芯片厂商建立了战略合作关系。更有甚者,直接打入半导体供应链内部,将芯片设计引入主机厂内部,这种模式称之为“OEM-Foundry-Direct”模式,代表企业有特斯拉、比亚迪等。

18)市场定位:选择什么样的主控芯片,首先要看该域控制器的市场定位:打算实现什么样的功能,用于配置在什么价位区间的车型上。

如果目标定位是做辅助驾驶,做一个L1~L2级的产品,而且是走量的,在选择芯片的时候对成本就很敏感。这样的域控产品,选择中低端芯片即可。

“如果说目标定位是打造一款L4级限定场景下的无人驾驶,那么客户可能更倾向于去打造一款定制化的产品。比如,定位做Robotaxi,打算走运营的一个模式,目的是想要先把算法打磨出来。它的量就不会特别大,那么选择芯片时,对成本相对就没那么敏感,但要求性能足够好,足够稳定。”

19)芯片的Roadmap:东软睿驰副总经理刘威提到:“从与芯片公司合作的角度来看,会看它是不是一个主流的芯片厂商,有没有连续的产品Roadmap。比如,有一些芯片厂商可能开发出了一款不错的芯片,但是后续没有更新换代。那么围绕该芯片来做域控制器,后续产品的迭代和升级会存在很大的问题。”

同样,均胜电子智能驾驶系统设计负责人李茂青也提到了相同的观点:“在域控制器系统设计中对于硬件方案的选型上除了关注芯片本身的功能性能外,还需要充分了解芯片公司的产品Roadmap,是否有灵活的家族化芯片系列,后续的芯片能不能PIN to PIN地在硬件平台上升级,继而可以在提升硬件性能的同时降低开发成本?”

20)芯片的生态(工具链):芯片整个软件的工具链或者对一些算法的开发是不是能满足客户的需求。也就是说芯片的生态怎么样,是否具备一个良好的生态系统能够支撑客户做可落地化的开发,也是主机厂或Tier1在选择芯片时候的重要考量因素之一。

英伟达的芯片生态在业界做的是比较领先的,它的生态包含了开发者、可用的应用软件、丰富的工具和库:

可为汽车领域提供丰富的软件算法人才;

在通用AI领域已训练出大量的算法模型及相关应用软件;

统一的硬件和底层软件接口架构(CUDA-X),可便捷的移植到汽车领域;

由于大量的用户使用,合作伙伴为CUDA平台贡献了大量的库和工具。

知行科技硬件研发总监解释道:“现在很多主机厂都在用英伟达的Orin芯片,除了它是一个大算力平台,另外一个重要的原因是它能提供整个软件的工具链,甚至一些底层的代码以及一些算法的代码都可以提供;开发者可以在上面做更多的适配,能够更好地开发出一款可以落地的高级自动驾驶计算平台。选择芯片,除了芯片本身,更多的是在选择一种生态。”

由如上对于自动驾驶域控制器选型过程中比较重要的几个因素,我们对市场主流的控制器芯片进行了统计分析得出如下分析结果对比表:

热点文章

-

2026北京车展 | 从“在中国为中国”到“在中国为全球”:安波福的跃迁与野望

2026-04-24

-

2026北京车展 | 维智捷:从汽车的“神经系统”到智能世界的“连接基础设施”

2026-04-24

-

2026北京车展:耐世特汽车系统以M³诠释线控运动控制新阶段

2026-04-27

-

2026北京车展 | Yandex Auto携全新AI车载平台概念精彩亮相

2026-04-26

-

聚力启新 智行未来:欧摩威以中国创新赋能全球出行

2026-04-30

-

2026北京车展零部件集锦|电池与电驱动篇

2026-04-29

-

2026北京车展零部件集锦 | 智能化与计算平台篇

2026-04-29

评论

加载更多